Figure 8.18

Dalam sistem digital, pengolahan dan distribusi data menjadi aspek penting yang harus diatur secara efisien agar komunikasi antar bagian sistem dapat berjalan dengan baik. Salah satu perangkat logika kombinasi yang berperan dalam distribusi sinyal adalah demultiplexer. Demultiplexer, atau sering disingkat DEMUX, merupakan rangkaian logika yang berfungsi untuk menyalurkan satu input ke salah satu dari beberapa output yang tersedia, berdasarkan sinyal kontrol atau select line.

Berbeda dengan multiplexer (MUX) yang bertugas memilih salah satu dari beberapa input untuk dikirim ke satu output, demultiplexer bekerja sebaliknya: ia menerima satu input data dan mengarahkannya ke salah satu dari banyak output, tergantung pada kombinasi dari sinyal seleksi yang diberikan. Dengan demikian, demultiplexer dapat dianggap sebagai “pembagi jalur” dalam sistem logika digital.

3. Or Gate

OR gate adalah salah satu gerbang logika dasar dalam sistem digital yang menghasilkan output logika tinggi (1) jika salah satu atau lebih input-nya bernilai tinggi (1). Output hanya akan rendah (0) jika semua input bernilai rendah (0).

4. Not Gate

NOT gate, atau disebut juga inverter, adalah gerbang logika dasar yang berfungsi untuk membalikkan keadaan logika dari input-nya. Jika input bernilai 1 (HIGH), maka output-nya akan menjadi 0 (LOW), dan sebaliknya.

1. Pengertian Demultiplexer

Demultiplexer merupakan kebalikan dari multiplexer (MUX). Jika multiplexer berfungsi untuk memilih satu dari banyak input dan mengarahkannya ke satu output, maka demultiplexer memilih satu dari banyak output dan mengarahkan sinyal input ke output tersebut.

2. Fungsi Dasar Demultiplexer

Demultiplexer memiliki satu input data utama (D), beberapa output (Y0, Y1, Y2, ..., Yn), dan sejumlah jalur seleksi (S0, S1, ..., Sn). Kombinasi biner dari sinyal seleksi menentukan ke output mana data input akan diarahkan. Hanya satu output yang akan aktif pada satu waktu, sesuai dengan nilai dari jalur seleksi, sedangkan output lainnya akan berada dalam keadaan logika rendah (0) atau tidak aktif.

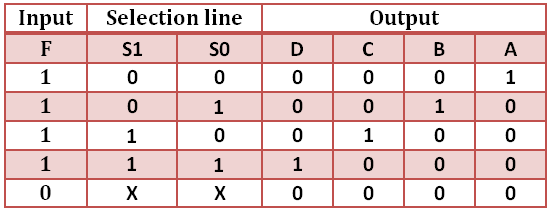

3. Tabel Kebenaran Demultiplexer 1-to-4

4. Persamaan Logika Demultiplexerr 1 to 4

Input = I

Select Line: S1, S0

Output: D0, D1, D2, D3

Maka persamaan logika outputnya:

D0 = I • S1' • S0'

D1 = I • S1' • S0

D2 = I • S1 • S0'

D3 = I • S1 • S0

Keterangan:

• = AND

' = NOT (invers)

Dengan kata lain, input I akan diarahkan ke salah satu dari 4 output tergantung nilai seleksi S1 dan S0.

5. Implementasi dan Komponen

Demultiplexer dapat diimplementasikan menggunakan gerbang logika dasar (AND, NOT, dan OR), atau menggunakan IC demultiplexer seperti:

- IC 74139 (Dual 2-to-4 line DEMUX)

- IC 74138 (3-to-8 line DEMUX/Decoder)

Dalam sistem digital modern, demultiplexer juga dapat direalisasikan dalam bentuk perangkat lunak atau dikodekan di perangkat logika terprogram seperti FPGA atau CPLD menggunakan bahasa VHDL atau Verilog.

6. Aplikasi Demultiplexer

- Sistem komunikasi digital: Untuk mengarahkan data dari satu jalur ke beberapa jalur tujuan

- Distribusi sinyal: Menyalurkan satu sinyal ke beberapa perangkat, seperti layar, sensor, atau aktuator

- Pengendalian tampilan: Mengendalikan segmen-segmen LED atau display dari satu jalur kontrol

- Sistem memori: Untuk mengaktifkan salah satu dari beberapa lokasi memori

- Download File HTML klik disini

- Download File Rangkaian figure 8.18 klik disini

- Download Datasheet And Gate klik disini

- Download Datasheet Or Gate klik disini

Komentar

Posting Komentar